ذخیره سازی و انتقال داده ها در یک مدار دیجیتال از اهمیت بالایی برخوردار است و به همین دلیل شیفت رجیستر ها ساخته شده اند تا ما را به اهدافمان در ساخت پروژه های مدار دیجیتالی برسانند.

استفاده درست از شیفت رجیسترها و انتخاب مناسب میان انواع پیکربندی آن ها ضرورت آشنایی کامل با عملکرد هر نوع را به همراه دارد.

در این مطلب ضمن معرفی این مدار، انواع پیکربندی آن را نیز مورد بررسی قرار خواهیم داد.

دعوت می کنیم تا پایان این مطلب با ما همراه باشید.

1# شیفت رجیستر چیست؟ (Shift Register)

شیفت رجیستر یک مدار منطقی ترتیبی است که برای ذخیره سازی و انتقال داده های باینری کاربرد دارد.

به زبان فارسی به شیفت رجیسترها، ثبّات انتقال دهنده نیز گفته می شود.

Shift Register نوعی مدار فایفو (FIFO) است که تک تک داده های بیت ورودی را متناسب با ساختار درونی اش به سمت خروجی جابجا می کند.

FIFO مخفف شده عبارت First In First Out است به این معنا که خروج داده ها به ترتیب ورود آن ها صورت می گیرد.

از مدارهای فایفو برای بافر کردن (ذخیره سازی موقت) و کنترل جریان داده از سخت افزار به نرم افزار در مدارهای الکتریکی استفاده می شود.

برای ساخت شیفت رجیسترها از لچ (Latch) یا فلیپ-فلاپ (Flip-Flop) استفاده می شود تا داده های باینری را ذخیره سازی کنند.

یک المان لچ وظیفه ذخیره یک بیت داده در یک زمان مشخص را دارد.

بر این اساس برای ذخیره سازی چند بیت داده در یک زمان به چند لچ نیاز است.

شیفت رجیستر ها از ترکیب سریالی لچ ها در کنار یکدیگر به وجود می آیند.

چیدمان سریالی لچ ها این امکان را به وجود می آورد که خروجی هر لچ به عنوان ورودی لچ بعدی عمل کند.

در نتیجه جابجایی داده ها در داخل مدار با ثبات لازم صورت می گیرد.

معمولا شیفت رجیسترها به صورت یک آی سی ساخته می شوند.

2# انواع پیکربندی Shift Register

تا اینجا با مفهوم شیفت رجیستر و کاربرد آن آشنا شدیم.

موضوع مهم دیگری که در زمینه پیکربندی مدارها باید مدنظر قرار دهید، جهت انتقال داده در لچ ها است.

انتقال داده بین لچ ها از چپ به راست، راست به چپ یا دو جهته صورت می گیرد.

باید به این نکته اشاره کنیم که داده های ورودی به مدار می توانند به صورت سریالی یا موازی به آن داخل یا از آن خارج شوند.

مفهوم ورود و خروج سریال به این معنا است که هر بیت از یک داده چندبیتی در یک پالس ساعت (Clock) وارد مدار شده و یا از آن خارج می شود و

در پالس ساعت بعدی نوبت به بیت بعد می رسد.

مفهوم ورود و خروج موازی به این معنا است که به ازای هر پالس ساعت همه بیت های یک داده چندبیتی به طور همزمان وارد مدار شده و یا از آن خارج می شوند.

بر این اساس حرکت بیت ها در مدار یک شیفت رجیستر با چهار پیکربندی گوناگون صورت می گیرد:

1-2# شیفت رجیستر SISO (سیسو)

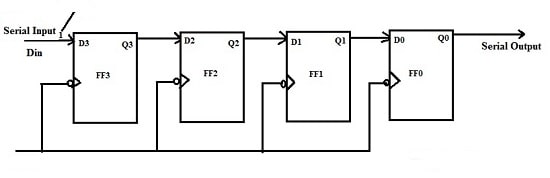

در شیفت رجیستر Serial-in Serial-out (SISO) بیت ها به صورت سری وارد و خارج می شوند.

همان طور که در تصویر زیر مشاهده می کنید، خروجی هر فلیپ فلاپ (FF) به عنوان ورودی FF بعدی عمل می کند.

در این تصویر ورودی ها با حرف D و خروجی ها با حرف Q نشان داده شده اند.

نهایتا یک خروجی نیز به صورت سریال از سمت راست حاصل می شود.

SISO به دلیل برخورداری از سه اتصال، ساده ترین نوع پیکربندی را در بین مدارهای مختلف دارد.

به طور مثال در صورتی که یک داده 4 بیتی ورودی مانند 1011 داشته باشیم و فرض کنیم که

همه فلیپ فلاپ ها ریست شده اند و خروجی تمام آن ها 0 است.

در زمان اولین کلاک ساعت عدد 1 وارد شیفت رجیستر شده و یک 0 از سمت راست آن یعنی Q0 خارج می شود.

با کلاک بعدی عدد 1 دوم وارد شیفت رجیستر شده و همه اعداد قبلی یک واحد به سمت راست شیفت پیدا می کنند و خروجی Q3 و Q2 مساوی 1 بوده و

یک صفر دیگر از خروجی شیفت رجیستر خارج می شود.

به همین ترتیب تمام اعداد ورودی بعد از گذشت 4 کلاک پالس شروع به خارج شدن از شیفت رجیستر به صورت سریال می کنند.

احتمالا برای شما هم سوال شده که با توجه به اینکه داده ها به همان ترتیب ورودی به صورت سریال خارج می شوند، کاربرد این نوع شیفت رجیستر چیست؟

از این مدار برای ذخیره سازی موقت اطلاعات، استفاده می کنند.

به این ترتیب می توان نوعی تاخیر زمانی را در اجرای داده ها برای اعمال کنترل بیشتر رقم زد و

این تاخیر زمانی را با استفاده از تعداد فیلپ فلاپ ها یا مدت زمان هر کلاک تنظیم کرد.

2-2# شیفت رجیستر SIPO (سیپو)

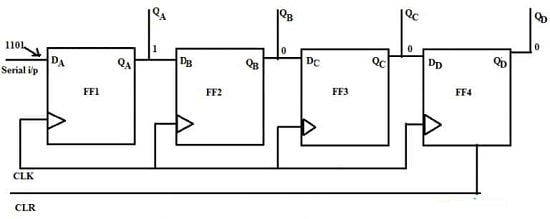

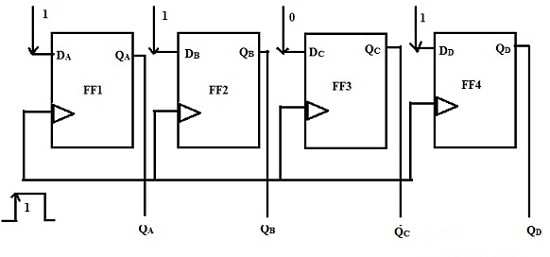

در شیفت رجیستر Serial-in Parallel-out (SIPO) بیت ها به صورت سریال وارد و به صورت موازی خارج می شوند.

در تصویر زیر یک مدار چهار بیتی سیپو به نمایش در آمده است.

فرض کنید در ابتدا تمام فلیپ فلاپ ها از FF1 تا FF4 ریست می شوند.

در نتیجه خروجی از QA تا QD همگی روی سطح منطقی صفر باقی می مانند تا هیچ داده خروجی موازی وجود نداشته باشد.

به عنوان مثال فرض کنید یک داده 4 بیتی ورودی مانند 1101 را به عنوان ورودی به این مدار اعمال می کنیم.

اگر پالس ساعت اول 1 را به فلیپ فلاپ FF1 وارد کنیم، خروجی QA تبدیل به 1 می شود.

در حالی که خروجی سایر بیت ها از QB تا QD صفر باقی می ماند.

در نتیجه خروجی کلاک پالس اول به صورت 1000 خواهد بود.

پالس ساعت دوم، خروجی FF1 را به صفر و خروجی QB را به یک تغییر می دهد.

سایر خروجی ها نیز روی صفر باقی می مانند.

در نتیجه خروجی داده دوم به صورت 0100 خواهد بود.

به همین ترتیب خروجی داده سوم و چهارم نیز به ترتیب برابر با 1010 و 1101 خواهد بود.

در نهایت با چهارمین کلاک، داده 1101 به صورت کامل در خروجی شیفت رجیستر قرار می گیرد.

از جمله مهم ترین کاربرد های این شیفت رجیستر می توان به موارد زیر اشاره کرد:

- ذخیره سازی داده های موقت به عنوان شمارنده جانسون رینگ (Johnson Ring)

- مبدل داده ها از سریال به موازی

- رمزگذاری و رمزگشایی داده ها

- ردیابی داده ها

3-2# شیفت رجیستر PISO (پیسو)

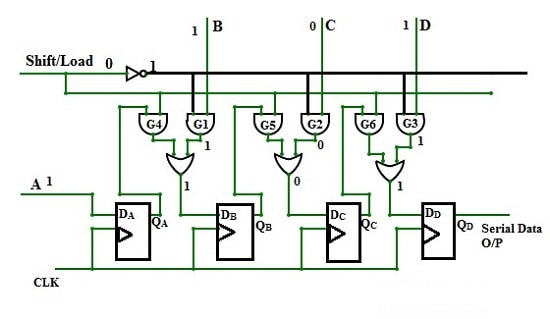

در شیفت رجیستر Parallel-in Serial-out (PISO) بیت ها به صورت موازی وارد و به صورت سری خارج می شوند.

عملکرد این مدار کاملا عکس شیفت رجیستر سیپو است.

در این نوع شیفت رجیستر همانطور که مشاهده می کنید علاوه بر فلیپ فلاپ ها از گیت های منطقی نیز استفاده می شود.

در تصویر فوق، داده ورودی به پین های ورودی شیف رجیستر از DA تا DD در زمان واحد وارد می شود.

سپس با هر کلاک پالس یک بیت از داده ها به صورت سریال از مدار خارج می شود.

بر این اساس برای بارگذاری داده ها نیازی به پالس ساعت به صورت موازی وجود ندارد.

در مقابل باید 4 پالس ساعت موازی برای خروجی اطلاعات در نظر گرفته شود.

این مدار به عنوان مبدل داده ها از موازی به سریال مورد استفاده قرار می گیرد.

به همین دلیل می تواند برای ایجاد تاخیر زمانی در مدارهای دیجیتال کاربرد داشته باشد.

در عمل معمولا از این مدار برای خواندن تعداد زیادی بسته سوئیچ در یک تراشه روی چند پایه استفاده می شود.

همچنین در تراشه حافظه، این شیفت رجیستر برای خواندن داده ها کاربرد دارد.

4-2# شیفت رجیستر PIPO (پیپو)

در شیفت رجیستر Parallel-in Parallel-out (PIPO) بیت ها به صورت موازی وارد و خارج می شوند.

از نظر کارکردن تقریبا مشابه با مدارد سیسو است و برای ذخیره سازی موقت یا تاخیر زمانی در داده ها کاربرد دارد.

در این مدار نیز داده ها به صورت موازی در پین های ورودی بارگذاری می شوند.

برای هر یک از پین های ورودی، یک پین خروجی به صورت متناظر تعریف می شود.

داده های ورودی به صورت مستقیم به پین های خروجی متناظر خود انتقال پیدا می کنند.

این مدار ساختمان ساده ای دارد و استفاده از آن نیز خیلی راحت و سریع امکان پذیر است.

تاخیر زمانی ایجاد شده در این نوع از شیفت رجیسترها معادل یک پالس ساعت است و در صورتی که داده ای مانند 1001 داشته باشیم و

همه فلیپ فلاپ ها ریست باشند، بعد از اولین کلاک پالس در خروجی داده 1001 را خواهیم داشت.

تنها نقطه ضعف این مدار، قدرت نه چندان زیادی جریان خروجی آن است.

|

نظرتون درباره این مقاله چیه؟

ما رو راهنمایی کنید تا اون رو کامل تر کنیم و نواقصش رو رفع کنیم.

توی بخش دیدگاه ها منتظر پیشنهادهای فوق العاده شما هستیم.