از آنجایی که ترانزیستورها یکی از پر استفاده ترین قطعه های الکترونیکی هستند، آشنایی با انواع آن ها برای هر مهندسی ضروری است.

ترانزیستور jfet یکی از انواع مهم این قطعات است که برای موارد آنالوگ بسیار کاربردی است.

در این مقاله سعی داریم با مشخصات این تجهیز، نحوه عملکرد و مزایای آن آشنا شویم.

#1 مشخصات ترانزیستور JFET

|

ترانزیستور Junction Field Effect Transistor یک نوع از ترانزیستورهای اثر میدان است.

ترانزیستورهای معمولی (BJT) یک وسیله کنترل جریان خروجی از طریق جریان هستند.

در حالی که ترانزیستور JFET یک وسیله کنترل جریان خروجی از طریق ولتاژ است.

ترانزیستور JFET یک وسیله سه ترمینال است که در آن یکی از ترمینال ها می تواند جریان بین دو ترمینال دیگر را کنترل کند.

JFET ها مانند نوع دیگر آن MOSFET دارای سه ترمینال هستند.

- Gate (دروازه)

- Drain (تخلیه)

- Source (منبع)

در ترانزیستور JFET جریان بین D و S را می توان با ولتاژ gate-source کنترل کرد.

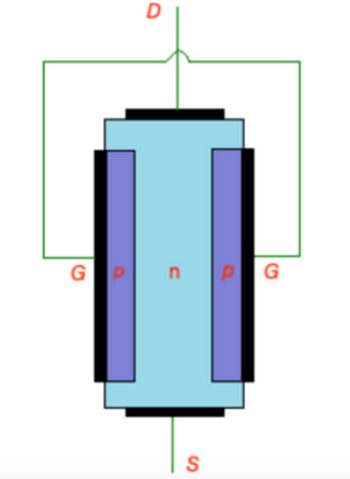

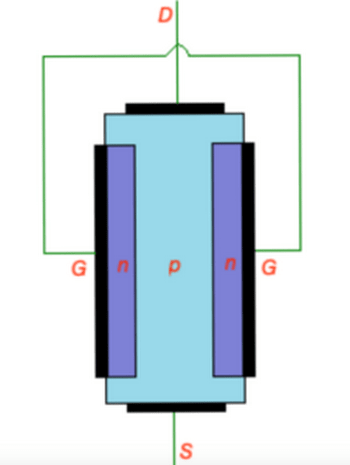

ساختار ترانزیستور JFET در شکل زیر نشان داده شده است.

ترانزیستور jfet نوع n

ترانزیستور JFET نوع n شامل نیمه هادی نوع n با مناطق نوع p دوپ شده به مقدار زیاد است.

منظور از دوپ شدن وارد کردن عمدی ناخالصی ها به یک نیمه رسانا به منظور تعدیل خصوصیات الکتریکی، نوری و ساختاری آن است.

در حقیقت یک نیمه هادی که به مقدار زیاد دوپ شده باشد بیشتر مانند یک رسانا عمل می کند.

#2 مزایای ترانزیستور JFET

JFET یک مؤلفه اساسی برای کنترل فشارهای ولتاژ در سیستم های الکترونیکی آنالوگ است.

می توان از JFET به عنوان کنترل ولتاژ یا به عنوان سوئیچ استفاده کرد یا حتی با استفاده از JFET تقویت کننده ساخت.

ترانزیستورهای JFET همچنین به عنوان جایگزین BJT ها یک نسخه کارآمد در مصرف انرژی هستند.

JFET مصرف برق کم و اتلاف انرژی نسبتاً کمتری دارد، بنابراین بازده کلی مدار را بهبود می بخشد.

همچنین امپدانس ورودی بسیار بالایی را ارائه می دهد که یک مزیت اصلی نسبت به BJT است.

امپدانس ورودی که همان مقاومت ورودی است، یک پارامتر بسیار مهم در طراحی تقویت کننده کننده های ترانزیستوری است.

#3 انواع ترانزیستور های JFET

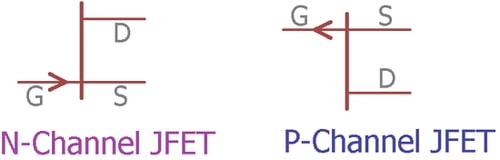

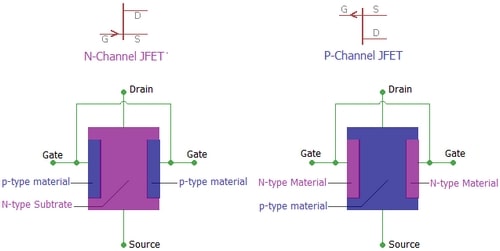

مانند ترانزیستور ماسفت، JFET نیز دارای دو زیر گروه N-Channel و P-Channel است.

مدل شماتیک هر دو گروه N-Channel و P-Channel را در شکل زیر مشاهده می کنید.

در شکل بالا جهت فلش ها انواع ترانزیستور JFET را مشخص می کنند.

فلشی که به سمت gate اشاره دارد نوع JFET N-Channel است و از طرف دیگر فلشی که از gate خارج می شود نشانگر نوع JFET P-Channel است.

این فلش همچنین حاکی از قطبیت اتصال P-N است که بین channel و gate شکل گرفته است.

جالب است که در زبان انگلیسی حفظ کردن آن با این علامت که فلش دستگاه N-Channel به داخل “Points in” اشاره دارد آسان است.

در هر دو مدل جریان جاری شده از طریق Drain و Source به ولتاژ اعمال شده به ترمینال Gate وابسته است.

در JFET N-Channel، ولتاژ Gate منفی است و در JFET P-Channel ولتاژ Gate مثبت است.

در تصویر بالا می توانید ساختار اولیه JFET را مشاهده کنید.

در ترانزیستور N-Channel JFET مواد نوع P در بستر نوع N قرار گرفته است در حالی که

نظرتون درباره این مقاله چیه؟

ما رو راهنمایی کنید تا اون رو کامل تر کنیم و نواقصش رو رفع کنیم.

توی بخش دیدگاه ها منتظر پیشنهادهای فوق العاده شما هستیم.

سلام و خسته نباشید بسیار عالی …کاربردی…شیوا و رسا و قابل درک….سپاس بسیار از زحماتتون

با سلام خدمت شما جناب جلیلیان بزرگوار

ممنون از همراهی و محبت و انرژی که به تیم نماتک میدهید برای ادامه ی این مسیر و محقق شدن اهداف نماتک.

آرزوی موفقیت براتون داریم

سلام.واقعا از زحمات شما صمیمانه تشکر دارم.خدا خیرتون بده.

سلام

ممنون از محبت و بزرگواری تون

موفق باشید

نتونستم بدون تشکر رد بشم صمیمانه از سخاوتمندی شما واسه این مطالب خوبتون ممنونم

سلام مهندس

ممنون از لطف و محبتی که به مجموعه ما دارید.

مایه افتخار و سربلندی ماست که این مطالب برای شما مفید واقع شدن.

همواره موفق باشید